제목: [Intel] 엣지 AI SW 아카데미

부제목: 12일차

일정: 2023.11.10(금)

수업 내용:

- C언어 프로그래밍

- Micro Processor 원리

- Atmel사의 8bit Micro-controller

- KUT0128 Evaluation Board 기능과 특징

- IIC-BUS Programming

- External Interrupt 제어

목표:

Interrupt

- 마이크로프로세서는 한번에 하나의 프로그램(명령)만 실행 가능, 이때 긴급히 처리해야 할 프로그램이

있을 경우

- 현재 실행중인 프로그램을 중지하고 긴급한 프로그램의 실행을 끝낸 후 중지한 프로그램을 계속 실행

- 프로세서의 내/외부 장치가 프로세서에게 특정 이벤트(event)가 발생함을 알려서 이벤트를 처리하는

과정 (Event : Interrupt flag, 처리 : Interrupt service routine)

- 이벤트는 프로세서의 내부 장치나 외부 I/O 장치에서 비정기적으로 발생하기 때문에 Interrupt 처리를

통해 주변 장치의 서비스(이벤트 처리) 요청을 효율적으로 다룰 수 있음

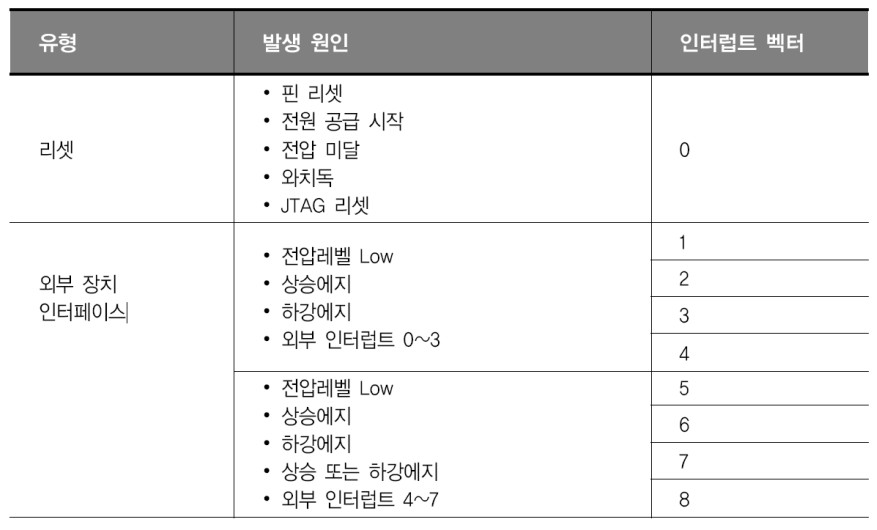

유형별 ATmega128 Interrupt 발생 원인

MCUCR(MCU Control Register)

• Bit 1 – IVSEL :

Interrupt Vector Select - 비트가 0이면 Interrupt Vector Table는 플래시 메모리의 시작에 위치 - 비트가 1이면 Interrupt Vector Table는 플래시 메모리의 부트 로더 섹션의 선두 위치로 이동 - 부트 로더의 선두 어드레스는 퓨즈 비트 BOOTSZ1..0에 의해 결정 - 이 비트에 새로운 값을 쓰기 위해서는 IVCE 비트를 우선적으로 1로 하고 4cycle 이내에 원하는 값 Write. 이 4cycle 동안 MCU는 인터럽트 금지상태

• Bit 0 – IVCE :

Interrupt Vector Change Enable - IVSEL 비트를 변경할 때 사용 - 1이 되고 4 사이클 후 또는 IVSEL에 값이 set 되었을 때 하드웨어적으로 clear - IVCE 비트에 1을 쓰고, 4사이클 이내에 IVSEL 비트에 원하는 값 Write

External Interrupt Mask register [ EIMSK ]

• EIMSK는 External Interrupt 를 enable 시키는 비트로 구성

• Bit 7~0-INT7~INT0 : External Interrupt enable bit - INT0~INT7 bit가 set 되어 있고 상태 레지스터 SREG의 I비트가 set 되어 있을 경우에 해당하는 외부 Interrupt enable - Interrupt trigger 방식은 EICRA와 EICRB 레지스터에 의해 설정

'[Intel] 엣지 AI SW 아카데미 > 펌웨어 프로그래밍 75hour' 카테고리의 다른 글

| [Intel] 엣지 AI SW 아카데미 14일차 (부산상공회의소 인력개발원) (1) | 2023.11.30 |

|---|---|

| [Intel] 엣지 AI SW 아카데미 13일차 (부산상공회의소 인력개발원) (0) | 2023.11.30 |

| [Intel] 엣지 AI SW 아카데미 11일차 (부산상공회의소 인력개발원) (1) | 2023.11.30 |

| [Intel] 엣지 AI SW 아카데미 10일차 (부산상공회의소 인력개발원) (0) | 2023.11.30 |

| [Intel] 엣지 AI SW 아카데미 9일차 (부산상공회의소 인력개발원) (0) | 2023.11.17 |