부제목: 22일차

일정: 2023.11.24(금)

수업 내용:

- UART 제어

목표:

UART 제어

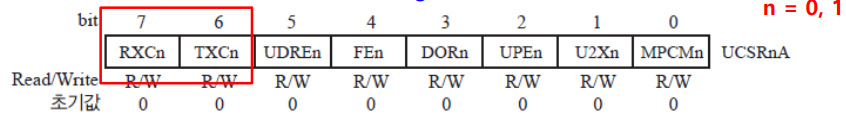

• UCSRnA (USARTn Control and Status Register A)

[7] RXCn (USARTn Receive Complete)

: 수신 완료 상태를 나타내는 플래그 비트

: UDRn (수신 버퍼)에 새로운 데이터가 수신될 때 마다 RXCn→1이 됨

이 때 수신 완료 인터럽트(USARTn Receive Complete Interrupt)를 발생

UDRn을 READ하면 RXCn→0으로 CLEAR 됨

[6] TXCn (USARTn Transmit Complete)

: 전송 완료 상태를 나타내는 플래그 비트

: 전송 쉬프트 레지스터에서 데이터가 전송되고

UDRn(전송 버퍼)에 새로운 전송 데이터가 write 되지 않으면 TXCn→1이 됨

이 때, 전송 완료 인터럽트(USARTn Transmit Complete Interrupt) 발생

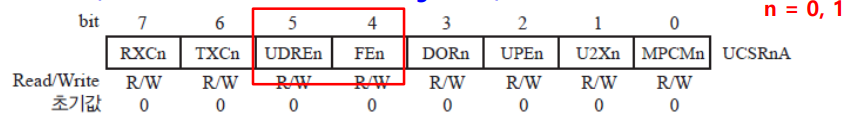

[5] UDREn (USARTn Data Empty)

: UDRn(전송 버퍼)에 새로운 데이터를 받을 준비가 되어 있으면

UDREn→1이 되는 플래그 비트, UDRn이 비어 있으면 UDREn→1이 됨

: UDREn→1일 때 전송 데이터 USARTn Data Register Empty Interrupt 발생

: UDRn에 새로운 데이터를 write 하면 UDREn→0으로 clear 됨

[4] Fen (USARTn Frame Error)

: UDRn에 데이트를 수신하는 동안 프레임 에러가 발생하였음을 나타내는 플래그

: 프레임 에러는 수신 데이터의 첫 번째 정지 비트가 0일 때 발생

: FEn은 UDRn을 read 할 때까지 유효하며

UCSRnA 레지스터를 write 하면 FEn→0으로 clear

[3] DORn (USARTn Data Over Run)

: USARTn이 수신 동작할 때 오버런 에러를 나타내는 플래그 비트

: 오버런 에러란 UDRn에 read 하지 않은 수신 데이터가 있는 상태에서

수신 쉬프트 레지스터(Receive Shift Register)에서 새로운 데이터 수신이 완료되고

다음 수신 데이터의 시작 비트가 검출될 때 발생

: UDRn을 read 때까지 유효하며 UCSRnA 레지스터를 write하면 DORn→0 clear

[2] UPEn (USARTn Parity Error)

: USARTn 패리티 에러 비트

: 수신하는 데이터에서 패리티 에러가 발생하면 UPEn→1

: UDRn을 read 때까지 유효하며 UCSRnA 레지스터를 write 하면 UPEn→0 clear

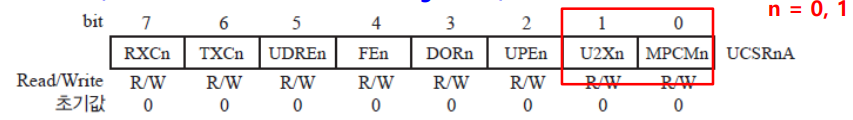

[1] U2Xn (USARTn Double Transmission Speed)

: U2Xn은 비동기 모드에서만 사용 가능한 비트

: 비동기 통신에서 U2Xn=1이면 USARTn의 통신 속도가 2배로 빨라짐

: 실제로는 USARTn의 clock 분주비를 16에서 8로 하여 통신 속도를 2배로 높임

[0] MPCMn (Multi-Processor Communication Mode)

: USARTn을 멀티-프로세서 통신 모드로 설정하는 비트

: 멀티-프로세서 통신 모드에서 어드레스 정보를 포함하지 않는 수신 데이터는

수신부에서 무시됨

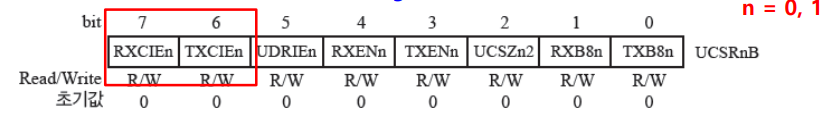

• UCSRnB (USARTn Control and Status Register B)

[7] RXCIEn (RX Complete Interrupt Enable)

: 수신 완료 인터럽트 enable 비트

: RXCIEn=1, SREG 레지스터의 I=1이면 UCSRnA 레지스터의 [7] RXCn→1 일 때

수신 완료 인터럽트가 발생하고 처리됨

[6] TXCIEn (TX Complete Interrupt Enable)

: 전송 완료 인터럽트 enable 비트

: TXCIEn=1, SREG 레지스터의 I=1이면 UCSRnA 레지스터의 [6] TXCn→1일 때

전송 완료 인터럽트가 발생하고 처리됨

[5] UDRIEn (Data Register Empty Interrupt Enable)

: 전송 데이터 레지스터 Empty 인터럽트 Enable 비트

: UDRIEn=1, SREG 레지스터의 I=1이면 UCSRnA 레지스터의 [5] UDREn→1일 때

USARTn 전송 데이터 레지스터 Empty 인터럽트가 발생하고 처리됨

[4] RXENn (Receiver Enable)

: 수신부가 동작하도록 Enable 하는 비트

: RXENn=1이면 RxDn 핀이 I/O 포트가 아닌 수신 단자로 사용 가능

[3] TXENn (Transmitter Enable)

: 전송부가 동작하도록 Enable 하는 비트

: TXENn=1이면 TXDn 핀이 I/O 포트가 아닌 전송 단자로 사용 가능

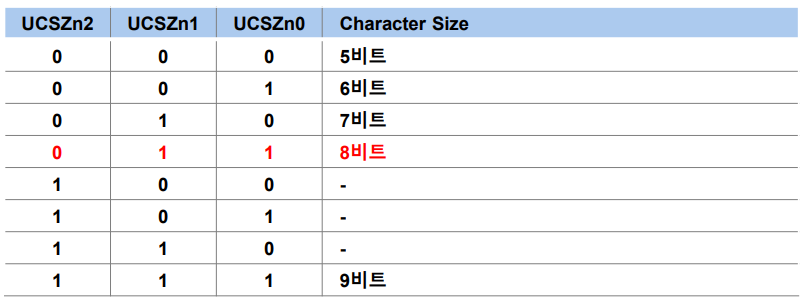

[2] UCSZn2 (Character Size)

: 통신 데이터 크기를 설정하는 비트

: UCSRnC 레지스터의 UCSZn1, UCSZn0와 같이 통신 데이터 크기를 설정하는 비트

[1] RXB8n (Receive Data Bit 8)

: 통신 데이터가 9비트일 때 9번째 비트(MSB)를 수신 받는 비트

: UDRn (수신 버퍼)을 read 하기 전에 반드시 RXB8n을 먼저 read해야 함

[0] TXB8n (Transmit Data Bit 8)

: 통신 데이터가 9비트일 때 9번째 비트(MSB)를 전송하는 비트

: UDRn(수신 버퍼)에 write 하기 전에 반드시 TXB8n을 먼저 write해야 함

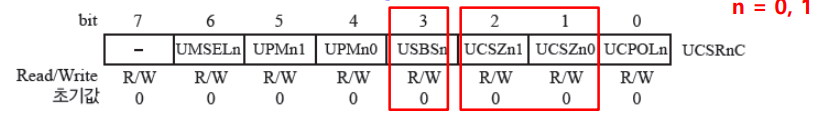

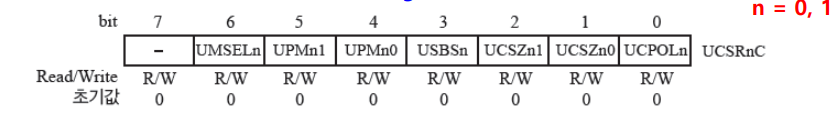

• UCSRnC (USARTn Control and Status Register C)

[6] UMSELn (USART Mode Select) : USART 모드 설정 비트

- 통신 모드 설정 비트

- 0이면 비동기 모드, 1이면 동기 모드가 설정

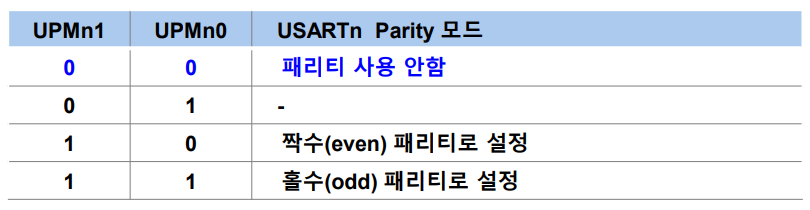

[5][4] UPMn (USART Parity Mode) : 패리티 모드 설정 비트

- 표와 같이 패리티 모드를 설정

[3] USBSn (Stop Bit Select) : 정지 비트 선택

- 0이면 1비트, 1이면 2비트가 설정

UCSRnB [2], UCSRnC [2][1] UCSZn1, UCSZn0(Character Size)

- 전송 데이터 비트 수 설정

[0] UCPOLn (Clock Polarity)

: UCPOLn은 동기 모드 통신에서 전송 데이터의 출력 시점과

수신 데이터의 입력 시점을 설정하는 비트

: UCPOLn=0일 때 전송 데이터는

XCKn clock의 rising edge에서 TXDn 핀으로부터 출력되고

수신 데이터는 XCKn clock의 falling edge에서 RXDn 핀으로 입력됨

: UCPOLn=1일 때는 반대로 됨

'[Intel] 엣지 AI SW 아카데미 > 펌웨어 프로그래밍 75hour' 카테고리의 다른 글

| [Intel] 엣지 AI SW 아카데미 24일차 (부산상공회의소 인력개발원) (1) | 2023.12.17 |

|---|---|

| [Intel] 엣지 AI SW 아카데미 23일차 (부산상공회의소 인력개발원) (1) | 2023.12.17 |

| [Intel] 엣지 AI SW 아카데미 20일차 (부산상공회의소 인력개발원) (1) | 2023.12.16 |

| [Intel] 엣지 AI SW 아카데미 19일차 (부산상공회의소 인력개발원) (2) | 2023.12.04 |

| [Intel] 엣지 AI SW 아카데미 18일차 (부산상공회의소 인력개발원) (0) | 2023.12.04 |